| Design | |||

| Modifications | |||

| Development | |||

|

[04-FEB-26] Below you will find circuit diagrams, data sheets, and other design files for the A3054 assembly. All our designs are free and open-source, with copyright protection presented in the GNU Public License, Version 3.0.

[10-APR-26] The A305401A Intraperitoneal Transmitter Circuit Board needs the following improvements following our experience with the A305402A Breadboard.

The A305402A Text Fixture Circuit Board needs the following improvements.

Chronological record of the development and production of the implantable Blood Pressure Monitor (A3054).

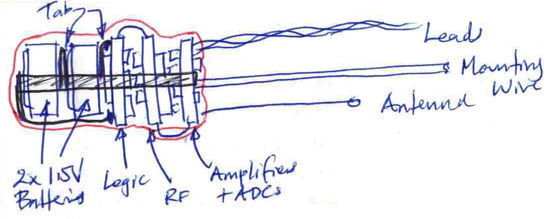

[04-FEB-26] Create web pages. Here is a sketch of the planned three-layer PCB rigid-flex circuit. The board consists of three circular sections joined by two flex cables. The flex cables between the rigid sections are just the right length so that they allow the rigid sections to fold over onto one another without leaving extra flex cable to jut out the side of the implant. On either end there are flex cables with flex connectors at the end. We use the left flex cable to power the circuit and program the logic chip. We use the right flex cable to test the amplifiers.

From left to right we have Section I, Section II, and Section III. Each lies within a 10-mm diameter circle and is squared off where the flex cable emerges from its side. The positive and negative battery tabs are on Section I. We tab-weld two 1.5-V SR936 1.5-V 9.5-mm diameter, 3.6-mm thick, 75 mAhr batteries together and to these two tabs to power the circuit, with the positive terminal resting on the logic chip and the negative terminal of the second battery on top. The two batteries are connected by their own tab. We cannot trust to contact to hold them together because the epoxy of encapsulation will penetrate between the two of them. Later, we fold the circuit onto itself, and secure the three layers together by tab-welding the two longer tabs on Section III to the negative terminal of the top battery.

Section I holds the magnetic sensor and transistor that put the circuit to sleep, the logic chip, a buck converter to generate the 1V2 logic power supply voltage, a linear regulator that produces 1.8 V, BMA423 accelerometer, TMP117 temperature sensor, and a converter that provides a battery voltage measurement.

We have a long discussion with ChatGPT about the possibility of using other logic chips, or ready-made micropower MCUs in place of our OSR8 in LCMXO2 FPGA. We consider using in place of the OSR8 the open-source PicoRV32 VHDL processor. This thirty-two bit alternative to our eight-bit processor takes up two thousand LUTs in its usual form, but can be stripped down to 750 LUTs, although in this state it has no memory interface. We consider how long the PicoRV32 will take to perform typical IPT tasks, such as add and accumulate samples, respond to interrupt, and generate random number. We estimate the PicoRV32 will take at least twice as long to perform these tasks, doubling our dynamic current consumption. An advantage of the PicoRV32 is the C-compiler toolchain we can use with it, but we enjoy writing OSR8 assembler, so we have no problem living without a compiler. Another big issue for the implant is the calibrated ring oscillator that turns on and off instantly. These are not available in any existing MCUs, which use RC oscillators, and none of the RC oscillators in the PIC chips we looked at will run at 5 MHz, only 4 or 8 MHz on either side. Our conclusion was that our existing LCMXO2, ring oscillator, and OSR8 is already the most energy-efficient design.

We would like to have spare logic on our device, but at the same time we want to get moving with a flex circuit that does not require microvias to transport IO signals out of a dense BGA. We decide to start our development of the IPT with the LCMXO2-1200ZE in QFN-32, which provides 21 IO pins, enough for the design we have in mind, and is easy to load by hand and work with. Despite the use of this larger package, we expect to be able to load a 1.2-V buck converter using made out of the ST1PS02D, its inductor and decoupling capacitor, on one side of the board, along with a 1.8-V linear regulator. The 1V8 will be used to power the accelerometer and temperature sensor, as well as the logic interfaces of our analog to digital converters, and our antenna switch. The logic chip will have all its I/O pins running off 1.8 V. This is adequate to control our five-bit tuning DAC, the VCO control input, the PE4259 RF switch, and the logic interfaces on our ADS7052 converters.

Section II will hold all RF circuits, while passing through logic signals and power for Section III. We will place near the VCO the five-bit resistor DAC required to provide the VCO's tuning voltage. Also on Section II will be the antenna switch and the crystal radio that produces the received power signal RP. The antenna matching network will be placed between the VCO and the switch, and the switch directly on the antenna.

Section III will hold four amplifiers, each consisting of a single micropower op-amp such as the MAX4464 a few passives, and a ADS7052 converter. Three of the amplifiers, those intended for ECoG, will in addition be equipped with an AC/DC selectors switch DG2012E. Through-hole pads will accommodate up to six biopotential leads, an antenna, and a mounting wire we will use during encapsulation. We would also like to include on this board 2.0-V and 1.0-V linear regulators to provide the amplifiers and converters with clean analog power. By this means, we hope to eliminate the noise caused by the irregularity of our telemetry system's transmission scatter. The dedicated converters eliminate noise generated by selecting one of four analog voltages with an analog switch. A last function we wish to apply to Section III is an electrode impedance measurement with an analog switch that applies a −10 mV step to the ECoG reference potential.

The total surface area of these three boards, counting both sides, is roughly 220 mm2, compared to 150 mm2 for our rounded-corner 12.5-mm square A3049 printed circuit board, which houses two amplifiers with dual op-amps and 3-pole low-pass filters. Our hope is that with the increased area and reduced complexity of the amplifiers, we will be able to fit all IPT circuits on the three-part circuit board.

[06-FEB-26] Working on the A305401A layout. We can fit all the planned components on Section I with 10-mm diameter. We have yet to draw a circuit diagram or route connections.

[10-FEB-26] We have the P3054 repository set up on GitHub. We first worked on the P3041 firmware, fixing instability in its interrupt manager, making changes, recompiling and checking for stability. We create OSR8V4 and perform some consolidation of logic and renaming which, in the end, makes not difference to the compiled code. We start P3054 with P3042 V3.1. The code takes up 1267 LUTs. We reduce the millisecond interrupt timers from sixteen bits to eight bits. Now 1195 LUTs. Eliminate the clock calibrator, which includes an eight-bit counter that counts TCK periods. Our plan is to measure the TCK frequency by watching the state of RCK through the top bit of the status register, thus moving the counter into software. The code remains 1195 LUTs, despite the removal.

[11-FEB-26] We cannot fit all the components we need onto three sections 10-mm diameter along with the antenna mounting hole, lead mounting holes, and tab pads on Section III. We resolve to add Section IV. On this fourth section we place some 0.5-mm tall resistors and one analog switch. These will all be on the top-side of the PCB, which will be folded so that it becomes the end wall of the assembly. There will be no parts on the other side of this section. Now that we have more space, we will make the rigid sections 0.6-mm thick rather than 0.8-mm thick. The flex sections will be 0.1-mm thick.

The flex circuits at the either end are 11-mm side, terminated with a ten-way 1-mm pitch single-sided flex plug. The plug on the left carries the seven signals required to program the logic chip, plus three test point signals. The plug on the right carries all the analog signals, of which there are six, as well as the analog power supplies and the Receive Power (RP) signal. The antenna signal enters on Section IV, passes along the flex connector to Section III, passes through Section III, and so to Section II where it is delivered to the RF switch. The length of these tracks will constitute our antenna before encapsulation. After encapsulation, we have this path folded twice, and then a bent cable antenna outside.

Section I still holds the logic, buck converter, accelerometer, temperature sensor, and oscillator. Section II holds the tuning DAC, VCO, crystal radio, antenna switch, and also the four ADCs for the biopotentials. Section III holds the amplifiers and their AC/DC switches. Section IV has pads for mounting holes, and also the resistors that immediately greet the incoming ECoG signals, as well as the impedance-measurement switch and its pair of resistors. We have ample space for soldering leads into six through-hole pads, antenna into its own pad, and the mounting wire. After soldering these wires into Section IV, we trim the understide. We must avoid contact between these components and the parts on Section II. Because Section II will provide epoxy-encapsulated components 1 mm tall, the two boards will be 1 mm apart. The resistors on Section III will be 0.5-mm tall. So we must trim the back side of Section IV so that nothing sticks out by more than 0.4 mm, in order to avoid contact and allow epoxy to provide insulation between the sections. If we load the eight wires with Section IV pressed flat on a flat surface, we should be able to solder them from the top side and avoid any wire protrusion on the other side. All the mounting holes are large enough to allow solder to flow around the leads, antenna, and mounting wire.

Adding 0.6 mm of epoxy and silicone to the outside of the assembly, all allowing for some indentation between the circuit boards, we estimate total volume will be around 1.8 ml. We calculate the mass by adding the mass of the two batteries to the mass of the rest of the circuit, using for the rest of the circuit a density of 1.2 g/ml. We arrive at 3.2 g total mass. Battery capacity is 85 mAhr = 3500 μA·d at 3.1 V.

We add a 2K×8 EEPROM to Section I, an M24C16-F from ST Microelectronics. We connect this device to the same I2C bus we are using with the BMA423 accelerometer and TMP117 temperature sensor. All three devices are powered by 1V8 and share the same SDA and SCL. We now have two locations for non-volatile storate. The TMP117 contains 48 bits of general-purpose non-volatilve memory (NVM). We can use sixteen bits for the device ID, four bits for a ring oscillator calibration, four bits for an RF center frequency calibration, and eight bits for a battery capacity counter. We still have sixteen bits left for power-up configuration. We will use the M24C16's 2 KByte of EEPROM to store the IPT's telemetry protocol. This program is written in OSR8 assembler and manages the IPT's behavior when the IPT is active. Upon waking, or in response to a command, the IPT will copy the NVM into its own program memory. When we activate the IPT, it executes the activity program either 1024 times per second, depending upon the IPT's configuration. The activity program reads sensors, accumulates samples, and manages transmission of telemetry messages, including introducing temporal scattering. We note that executing 1024 times per second is about as often as we can hope to do so with the OSR8 running at 32.768 kHz. When the interrupt occurs, the OSR8 will complete its current operation (1), jump to the interrupt location (2), jump to the interrupt routine (3), push accumulator (1), load 0x01 (2), enable TCK (3), boost (3). So that's 15 clock cycles just to start the interrupt in boost. We need another 9 to return from the interrupt. So just servicing the interrupt without any content costs us 24 clock cycles, and we have only 32 between interrupts. Assuming our activity program completes in under 300 clock cycles, it will take 2 clock cycles, leaving 6 clock cycles for the main loop to use to service incoming commands. Somewhere in here we have to fit sample transmission and scatter.

[12-FEB-26] From our OSR8 study of static current consumption, we expect the static current drawn by one of the LCMXO2-ZE devices from our 3.0-V battery at 37°C to be 39% of the typical value presented in Table 3.9 of the MachXO2 data sheet.

| Device | LUTs | RAM KBits | I_q (μA) Tabulated | I_q (μA) Implantable | Packages (Name, mm × mm) |

|---|---|---|---|---|---|

| LCMXO2-256ZE | 256 | 0 | 18 | 7.0 | QFN-32 5x5, ucBGA-64 4x4 |

| LCMXO2-640ZE | 640 | 18 | 28 | 11 | QFN-48 7x7 |

| LCMXO2-1200ZE | 1280 | 64 | 56 | 22 | WLCSP-25 2.5x2.5, WLCSP-36, 2.5x2.5, QFN-32 5x5 |

| LCMXO2-2000ZE | 2112 | 74 | 80 | 29 | WLCSP-49 3.2x3.2 |

| LCMXO2-4000ZE | 4320 | 93 | 124 | 48 | WLCSP-81 3.8x3.8, QFN-84 7x7 |

| LCMXO2-7000ZE | 6864 | 240 | 189 | 74 | NONE |

If we cannot fit our code into the 1200ZE, we will have the option of loading the 2000ZE in its place, and suffer an increase of 9 μA in our static quiescent current. For implants where we do not need the sophistication of the OSR8, such as an upgrade to our existing A3047, A3048, or A3049 SCTs, we could try the 256ZE with only 7 μA quiescent drawn from 3.0 V. Right now, the current consumption of the A3048 is 18 μA + 0.12 μA/SPS, of which 0.07 μA/SPS is the VCO during transmission, 0.01 μA/SPS is the DAC, 0.04 μA/SPS is the logic. The ADC contribution is negligible. If we add the quiescent current of the magnetic switch, op-amps, converter, and regulators, we might get 12 μA from the battery quiescent. Dynamic current consumption from logic will be at most that of an OSR8 plus ring oscillator, which is 1.2 mA * 7 μs = 0.0084 μA/SPS. Combined we get 12 μA + 0.09 μ/SPS. At 256 SPS this implies 35 μA. Operating life with CR1225 rises from the A3048's 41 days to 57 days.

[20-FEB-26] We have completed OSR8 V4.2. We removed eight instructions that we have never used. This size of the CPU by around 60 LUTs. We constrained the logic fully, adding default values for all signals in both combinatorial and synchronous processes. This increased the size of the code by around 100 LUTs. We removed integer types and replaced with unsigned and vector types. We simplified many expressions. We separated the ALU input multiplexer from the CPU into its own process. These changes reduced the size by around 40 LUTs. In the P3041 code, we fixed our asynchronous resets in the interrupt controller. We enhanced the boost controller so that it can start TCK and move immediately into boost. We added to the OSR8 an interrupt servicing output, which we now use to put the CPU immediately and automatically into boost when an interrupt starts, and out of boost when it ends. The P3041 code is now 1201 LUTs. We have 79 LUTs free. The A3054 does not need the A3041's sixteen-bit interrupt counters, nor its millisecond timer. It will not need the TCK calibrator because we have devised a way to calibrate TCK from within software by watching RCK and counting. When we remove these processes, the code shrinks by another 50 LUTs to about 1150 LUTs. We will have around 130 LUTs for A3054 peripheral functions, such as ADC readout.

[23-FEB-26] We are estimating the current consumption of the A3054. Suppose we digitize and accumulate samples from all four fourteen-bit ADCs at 1024 SPS. We now have instant boost and un-boost with FCK running for an average of 4 μs after we un-boost. We can ignore FCK current consumption outside the time required for completion of the interrupt. Using FCK to read out the ADCs, we can obtain a 14-bit sample in no more than 20 FCK cycles, or 2 μs. We estimate no more than 25 TCK clock cycles to read the sample and add to its 18-bit accumulator in RAM. We might be adding up to sixteen samples before transmitting. We use IX and IY to accelerate read and write. We have TCK = 5 MHz so that's 5 μs to read and accumulate. The read initiates the next conversion in the ADC. The ADC itself consumes 0.5 mA at 1 MSPS, so 0.5 μA at 1024 SPS. We have 7 μs of CPU in boost, consuming 1.2 mA from 1V2. With our 80% efficient converter, battery at 3.1 V, and 1V2 = 1.02 V, current from battery is 1.02 V / 3.1 V / 80% = 41% of 1V2 current. So our 1.2 mA is 490 μA from the battery. We need this current for 7 μs per sample per second, so 7 μs * 490 μA * 1/s = 3.4 nA/SPS = 3.5 μA to support 1024 SPS. Each active channel requires 0.5 + 3.5 = 4.0 μA for sampling.

At the end of the sampling interrupt we decide if we are going to transmit one of the channels. If we are going to transmit, we copy the 18-bit accumulator into an 18-bit transmit register and then shift left or right until we get the correct 16-bit sample. This might be the average of sixteen samples or a single 14-bit sample left-shifted twice so it is 16-bit. We set a random delay interrupt of 0-7 RCK cycles to produce transmission scatter. These tasks take another 25 clock cycles, or 5 μs, which is 2.5 nA/SPS transmitted. Our sample interrupt ends and the tranmit interrupt occurs a random time later. Right now, our boost controller does not allow us to leave boost during transmission. The transmission takes 7 μs at 10 mA from the battery directly for the VCO and about 10 μs at 1.2 mA from 1V2 for the CPU in boost. We have 7 μs * 10 mA * 1/s 70 nA/SPS for the VCO from the battery and 10 μs * 1.2 mA * 41% = 5 nA/SPS from the battery for the CPU, for a total of 75 nA/SPS transmitted.

The quiescent current of the LCMXO2-1200ZE at 37°C is 56 μA from 1V2. Add to this another 14 μA for the crystal radio, amlifiers, accelerometer, thermometer, and EEPROM, we get 70 μA. From the battery this will be 70 μA * 41% = 29 μA, say 30 μA. Combining this with the above 4.5 μA/Ch (per active input channel) and 75 nA/SPS transmitted we have:

I_a = 30 μA + 4.5 μA/Ch + 0.075 μA/SPS

Suppose we have one active channel at 256 SPS, our current is 53 μA, which is a little over the 48 μA maximum of the A3048S2. But here we are going to be adding four 14-bit samples to obtain a very fine 16-bit sample, far superior to the spikey sixteen-bit samples we obtain from the A3048. Now suppose we have two active channels at 512 SPS. Our current is 115 μA, which is less than the 22 + 1024 * 0.11 μA/SPS = 135 μA of the equivalent A3049 two-channel circuit.

[26-FEB-26] Schematic for A3054AV1 drawn. There are twenty-one programmable pins on the LCMXO2-1200ZE in QFN-32 we are deploying on the A3054AV1 as U4. We will use all of them. Four must be shared with the programming signals TMS, TDI, TCK, and TDO. These we assign to the D0-D3 bits of our five-bit tuning DAC, on the grounds that they will be loaded by at most 2 kΩ and driving them during programming will cause no harm. The programming cable will use the JTAG Enable pin, which we call PEN, on U4-26, to switch these outputs from their programmed to their programming functions. We have nineteen pins that are necessary for the functioning of the IPT and we use the two remaining pins for an indicator lamp, signal LED, and at test point, TP. The LED and XEN signals must be 3-V logic, so we assign these to IO Bank 3, which provides exactly two pins, and power VCC3 with VS ≈ 3.0 V, the switched battery voltage. The other three IO banks we power with 1V8 = 1.8 V. The core VCC we provide with 1V2 = 1.20 V on startup and later with the assertion of LV becoming 1.0 V.

[04-MAR-26] Layout of the A305401A complete. We had to use six layers in the rigid sections, but were able to manage with only two in the flex sections. We used one via in the flex sections to complete the layout, having determined from our fab house that vias in the flex sections are standard. The entire rigid-flex circuit is 73 mm from end to end and 11 mm high with its two flex cables. Once the IPT is programmed, calibrated, and configured, we will cut off the flex cables, leaving four 10-mm diameter sections joined by 3.5-mm flex cables.

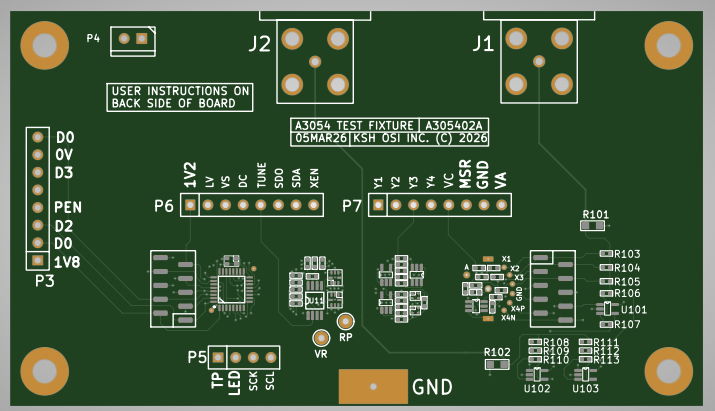

Before we make the rigid-flex A305401A we will make the rigid-only A305402A, which will include the A305401A layout on a 1.6-mm thick rigid board, along with two 10-way flex sockets, an eight-way programming plug, a two-way power plug, a BNC socket to bring in an analog signal for the IPT inputs, and various other pin headers for calibration and testing. This board will serve as a test of the IPT circuit, but in the future serve as our programming and calibration test fixture. Once our A305401A netlist has been double-checked against the schematic we will proceed with the A305402A layout.

[05-MAR-26] We complete the layout of the A305402A test fixture circuit board, which we will use to build the A3054X breadboard version of the IPT and the A3054TF test fixture for programming and quality control. There are many test points on the circuit board. Those marked in the larger font are available in the test fixture version, when we plug a rigid-flex IPT into the flex sockets on the left and right. Those marked in the smaller font will be available when we build the A3054AV1 circuit on the test fixture circuit board for our first tests.

In addition to a programming plug for the logic chip, a power plug for bench-top or battery power, and numerous test points, the test fixture provides two BNC sockets for delivering a differential signal and a common-mode signal to the A3054 amplifiers. These are DIN and CIN on the schematic S3054X_1.gif. We terminate DIN with 51 Ω and deliver through 1.0 MΩ to X1, X2, and X3, where the input impedance of 1.0 MΩ will divid the terminated signal by two. We take DIN and invert it with respect to VC. We assume that we will be delivering DIN, the differential input, with an offset of VC = 0.90 V, which we can do easily with our analog signal generator. We now have DINM and DIN, a differential signal about VC. We shift both of them downwards by CIN-VC and connect them to X4P and X4N. Now we can apply a true differntial signl to X4P and X4N as well as a true common mode signal, all without unplugging anything or reconnecting anything, under the control of our analog signal generator.

[16-MAR-26] We are waiting for the A305402 and going about securing all the parts we need to build the prototype on the test board. While welding batteries onto SCTs today, we started to re-think our plan to have the IPT hibernate on a magnet, but always be running when it is not attached to a magnet. After welding the battery taps on the IPT, we will encapsulate in epoxy, touch up epoxy, and coat twice with silicone. This process takes at least two days, and sometimes four days. During that time, the IPT will be awake and consuming 15 μA. We might lose up to 1.4 mAhr of battery life during encapsulation. Now, when we want to soak them in water to check the coating, we can leave them for another one to three days soaking while awake, or we might make a container with individual magnets in the bottom to hold the IPTs while we cover them with water to soak. There may be several more problems with our hibernation plan that we are as yet unaware of. The ISTs in which we first implemented the hibernation model had waking current of only 5 μA, so we concluded the loss during encapulation was tolerable. We may be better off adding a flip-flop to the sensor output so we can drive the mosfet switch on and off as we bring the magnet near.

[24-MAR-26] We receiver our A305402A boards. We load U1 and Q1 and 10 μF capacitors using paste and oven. Our SOT-723 footprint, which we copied from KiCad libraries, has a pin assignment that does not agree with our tradition, and as a result the transistor is connected incorrectly.

[25-MAR-26] Short Q1-1 to Q1-2 with a wire link. Load U2, we now have U1 (not used, but working), Q1 shorted, C1 = C3 = 10 μF, C2 = C4 = 1.0 μF, L1 = 2.2 μH. Load 10 kΩ from 1V2 to 0V. Have LV input floating. Connect 3.0 V to VB. Measure 1V2 = 1.01 V, VB current I_VB = 43 μA. Meanwhile, 1V2 current must be I_1V2 = 101 μA. We add 33 kΩ in parallel with our 10 kΩ load, adding 31 μA to I_1V2. We see I_VB increase to 57 μA. Differential conversion efficiency is 31 / (57 - 43) * 1.01 / 3.0 = 73%. Absolute efficiency, including magnetic sensor current, is 132 / 57 * 1.01 / 3.0 = 78%.

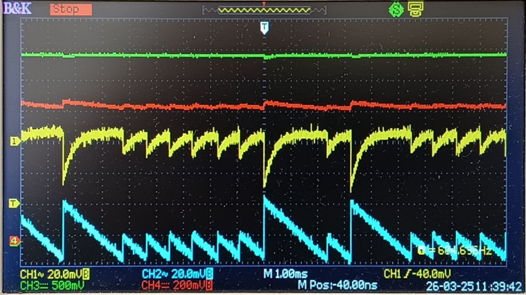

The battery voltage VB = VS on the circuit is stepping down when the converter connects its inductor to VS, while 1V2 steps up. These steps are usually 18 mV but sometimes 36 mV. Following a large step up, we have relaxation at 36 mV / 2.2 ms = 16 V/s as our 101 μA load drains C3, implying C3 is behaving like 101 μA / 20 V/s = 6.3 μF. We examing the AC-coupled VS and 1V2 as well as the switching side of the inductor. A 36-mV step up is one where the converter applies two pulses to its inductor rather than just one. This happens roughly 10% of the time. Otherwise, the converter, U2, applies one pulse and generates an 18-mV step up. When VS steps down 36 mV, 1V2 steps up 36 mV, which suggests the charge is being transferred from C1 = 10 μF to C3 = 10 μF with no loss.

When U2 connects L1 to VS, we see VS dropping as C1 discharges while 1V2 rises as C3 charges up. When the converter connects L1 to 0V, L1 continues to pump current into C3. After the second pulse on L1, we have U2-3 connected to 0V for 500 ns as it discharges its energy into C3. When U2 releases L1, the inductor still has some energy left, and drives its current through a Schottky diode in U2. When it is exhausted, L1 causes U2-3 to ring for a few cycles before settling to 1V2.

We load U3 and C4 and get 1V8. We load U4 and U4. We set up P3054 firmware, starting with the latest P3041. We remove stimulus code from ROM.asm and add a pulse on df_reg(1) to mark the main loop. We program U4. We see 1V2 = 1.20 V and I_VB = 38 μA with LV driven LO. Reprogram and drive LV HI. We now have 1V2 = 1.02 V and I_VB = 22 μA at 25°C. We see our pulse on TP showing the main loop execution. We warm to body temperature, I_VB increases to 28 μA.

[31-MAR-26] We abandon our "hibernate on a magnet" plan. We remove the 1V8 power supply, which eliminates a regulator and a capacitor. We use VS in place of 1V8 everywhere. We add a flip-flop in UDFN-6 package. We can now turn the A3054 on and off with a magnet, and we still have a mosfet switch. We move the oscillator to the bottom side of the IPT layout so it won't tilt the battery.

Meanwhile, we press on with the A3054X breadboard. We set frequency_low to 24 in ROM.asm. We try the auto-calibration of TCK and get TCK period varying from 163-184 ns with the ripple in 1V2. The entire message transmission is 6.06-6.82 μs. We have 50% reception. We replace the old divider-based ring oscillator with the new many-gate ring oscillator we developed for 1V2 = 1.0 V in the P3051 firmware. We delete the Clock Calibrator process from Main.vhd. Our compiled code is 1168 LUTs. We set fck_divisor = 24 and period of TCK is 197-227 ns. If we decrement or increment fck_divisor, the period is too short or too long. The variation is due to ±18 mV ripple in 1V2.

[01-APR-26] Our A3054X is using its multiplier to transmit the square of sample number, which we see on the Receiver Instrument. Our TCK is 212±15 ns, or ±7%. We have 36 mVppo ripple in 1V2. In place of P0603 2.2 μH for L1, we load P0805 4.7 μH. We now have TCK 216±10 ns with 20 mVpp ripple. Increase C4 to 20 μF, TCK is 218±4 ns, which is ±2%. Ripple in 1V2 is down to 10 mVpp. We drop transmit rate to around 105 SPS. Quiescent current is 33 μA with our 4.7 μH and 20 μF. With 4.7 μH and 10 μF, 35 μA. With 2.2 μH and 10 μF, 36 μA. With 2.2 μH and 20 μF, 35 μA, TCK is 217±6 ns, 1V2 ripple 16 mVpp. Go back to our P0805 4.7 μH and load 22 μF for both C1 and C3. Current is 32 μA, TCK is 223±5 ns, or ±2%. We examine the 1V2 ripple with a ×1 probe, 2.7 mV rms, 13 mVpp, but at the time of transmission, the value varies by 10 mVpp. We drop fck_divisor from 24 to 23 and now have TCK 194±4 ns. The drop in TCK period from fck_divisor 24 down to 23 is 13% when the decrease in the number of gates in the ring oscillator is only 4%.

Our A3054X is consuming 32 μA while transmitting 110 SPS and calculating a square for each sample. We remove the multiplication and instead just increment a register and transmit in place of both low and high bytes of the sample. With the removal of the multiplications, current consumption drops from 32 μA to 28 μA while sample rate remains 110 SPS. Each multiplication costs 36 nC from the battery. We increase sample rate to 185 SPS and current increases from 28 μA to 35 μA. The transmission cost is 0.093 μA/SPS. Extrapolating back to 0 SPS, the static current consumption at 25°C is 18 μA. P3054 commit 0b346e2.

Add crystal radio and comparator. Remove regular sample transmission. Current 22 μA at 0 SPS. The A3054X responds to a request for identification, but does not at first turn on its transmitter. We start again with ROM.asm copied from P3041. We disable the clock calibration. We change frequency_low to our value 24. We set the ID to 0xAA55 for its distinctive bit pattern. We restore the Stimulus Controller to Main.vhd and replace On Lamp (ONL) with LED. We put a dummy response in place for a battery measurement to give an apparent 3.0 V. We load a white LED for D3. Test all functions, everything working: transmit, stimulus, acknowledgements. We measure battery current versus sample rate and get a slope of 84 nA/SPS.

[02-APR-26] Load U7 TMP117, the temperature sensor. Add I2C code to ROM.asm, copying from P3051. Our program is now 2900 bytes. The total program memory is 4096 bytes. In the A3041, we use the bottom 2048 bytes for the main program and set aside the top 2048 bytes for the user program. We write a "ret" instruction to location 2048. We can no longer tolerate this "ret", so we comment it out. We are configuring and reading the temperature sensor. Firmware v1.3.

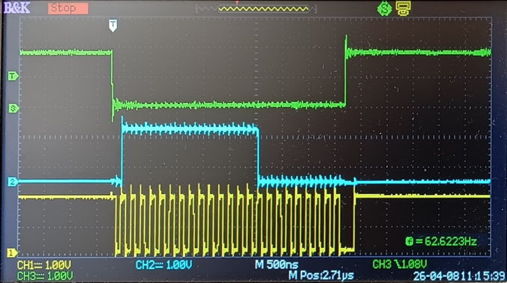

Our I2C interface is running at 5 MHz / 9 = 555 kHz when the maximum specified for the TPM117 is 400 kHz. But the sensor measurements are being read out correctly: we see 24.9°C. Here is an example of one of our SCL pulses on a single-bit read. Each instruction has the numer of CPU clock cycles next to it, and the CPU is running at 5 MHz.

ld (mmu_i2cZ0),A ; 3 ld (mmu_i2cZ1),A ; 3 ld (mmu_i2cZ0),A ; 3

The total time for the read is 490 clock periods including the call and return, or 98 μs. The ring oscillator and CPU together consume 1200 μA from 1V2, or 1200 μA * 1.02 V / 3.0 V / 80% = 510 μA from VB = 3.0 V. Each TMP117 readout requires 98 μs * 510 μA = 50 nC of charge. The readout cost of sampling is 50 nA/SPS. Add the transmit-only cost of 84 nA/SPS and we get 134 nA/SPS. Our actual cost is 140 nA/SPS, so we assume the extra 6 nA/SPS is consumed by the I2C interface and the TMP117 itself.

[03-APR-26] We use the TMP117 temperature sensor loaded on our A3054X to measure static current consumption versus temperature. We start by putting the A3054X in our oven, removing, connecting it to power and wrapping in insulation. We watch current consumption from the battery at 0 SPS then turn on transmission of the temperature measurement. To get the colder temperatures, we place two ice packs on either side of the A3054X and wrap with insulation.

The quiescent current at 0 SPS is the "wake current" of the IPT, in which it is awaiting commands but otherwise doing nothing. The wake current is around 34 μA at 37°C. We configure the TMP117 to provide a new measurement every 15.5 ms, which is its specified typical conversion time, and now we see noise on the temperature measurement we receive at 256 SPS. Current consumpton is around 220 μA, suggesting the TMP117 consumes 160 μA when producing 1 / 15.5 ms = 64 SPS. The TMP117 data sheet says current consumption during active conversion is typically 135 μA and the sensor is converting as fast as it can.

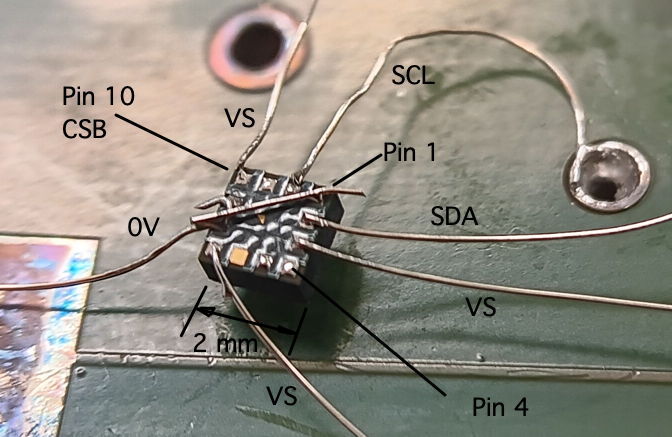

We load U6, the BMA423 accelerometer. We spend the day trying to get it to respond to our I2C bus. For a few seconds it responds at one point, then stops. We conclude that the device is not configuring for I2C because we failed to tie U6-10 CSB to VDD. The data sheet says that we can leave this pin "VDDIO or NC (float)" to get I2C instead of the SPI interface, but recommends we connect it to VDDIO. In their application circuits, CSB is connected to VDDIO for I2C. So we solder 125-μm bare silver wires to one of the devices and make three connections to 0V, three connections to VS, and connect SCL and SDA as well.

We still fail to communicate correctly. The device does not respond nor acknowledge our I2C cycles when we have probes on SDA and SCL. We are trying to read register 0x00, the chip_id = 0x13. We are transmitting 32767, which means we are reading 0xFFFF from SDA. In our software, we add 0x1000 to the value we read from the accelerometer so as to offset the accelerometers two's compliment range −32768..+32767 to our unsigned sixteen-bit range 0-65535. When we remove our probe from SCL, however, something starts driving SDA. We see the bits in our trace of SDA alone. We are transmitting a value 37632. We are reading 0x13 from register 0x00 into our top byte and a reserved byte from register 0x01 into our bottom byte. Assuming the reserved byte is zero, we expect to get (19 * 256) + 32768 = 37632. So it appears we are communicating with the BMA423 now that we have CSB = VS. We remove the wired chip, clean, dry, and return to our TMP117 either shut down or converting at 64 SPS with 256 SPS transmitted. When shut down, current is 23 μA. In the S3054_1 schematic, we connect U6-10 (CSB), U6-4 (ASDA), and U6-11 (ASCL) to VS. The latter two we connect so we can get to U6-10, and the data sheet says we can connect these to VDD if we are not using the secondary interface.

[07-APR-26] Load U8, M24C16, our 2K × 8 EEPROM. Its I2C device address is 0x50 for the first 256 bytes and 0x57 for the eigth. We are able to write 0xA5 = 165 to byte zero on start-up and then read it back again repeatedly for transmission. The second byte we read is 0xFF, which is consistent with erasing a sixteen-bit page and writing the first byte with 0xA5. The next fifteen bytes will be 0xFF. We are transmitting 0xA5FF = 42495, which is what we see in our Receiver Instrument.

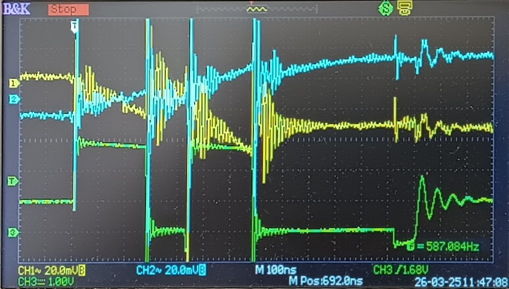

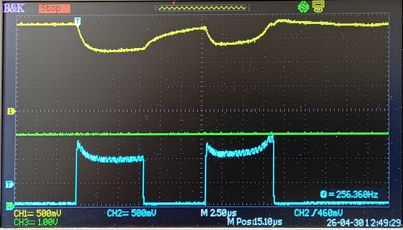

[08-APR-26] We load U12, ADS7052, the first of four 14-bit micropower converters. We connect VA to VS because we don't have the VA regulator loaded. We have nothing connected to the ADC input. We read the ADC and transmit. We see value 16383 = 0x3FFF. We connect the ADC input to 0V with a 10-MΩ probe and the value drops to zero. The ADC readout is shown below for 0x3FFF. The readout is driven by FCK at 10 MHz. We have SCK and !ADC1 HI during idle. At the start of the readout, !ADC1 goes LO. After 100 ns, SCK goes LO as well, and SCK proceeds to run at 5 MHz for 17 rising edges, then goes LO. We see the ADC producing a 0 on SDO until the first rising edge on SCK, fourteen 1s on the first fourteen rising edges, and three zeros on the final three rising edges. Now SCK remains LO and !ADC1 goes HI. Not seen in the picture is SCK going HI again some a little later. The entire readout takes 3.3 μs.

At power-up, we will get all four ADCs to self-calibrate by performing a readout of twenty-four bits, which requires twenty-three rising edges on SCK before we unassert ADC1. The picture below shows a calibration cycle. We see nine zeros being clocked from the ADC at the end of the cycle. At startup, we sould see all zeros from the ADC, but this is not a startup calibration, it's a calibration cycle performed after we have sampled from the ADC. This calibration cycle as shown will not, in fact, provoke a self-calibration. Only the first access after power-up can we used for self-calibration with twenty-four bit readout. If we want to self-calibrate again, we must read out sixty-four bits. Our firmware does not support re-calibration at the moment, only calibration at start-up. At the end of the cycle we see !ADC1 going HI and SCK going HI after another 200 ns.

When we read the ADC, the data is available in 3.3 μs. But the ADC readout state machine, as it exists now, will not be available to read another ADC until a total of 4.5 μs after the start of the access. Given that our CPU must fetch and store the sample, this extra 1.2 μs, which is 6 CPU clock cycles at TCK = 5 MHz, will not slow us down.

Load remaining three ADCs, the VA and VC regulators, amplifiers and analog switches. We control the ADCs with an eight-bit register in which we have functions for six of the bits. Bits zero and one specify the ADC. Bit two tells the ADC Controller to begin an SPI bus access. Bit three tells the controller to continue the access for twenty-four bits, but not to store those bits in the ADC data register. With bit three cleared, the controller stores fourteen bits in the data register. With bit four set, the controller shifts the fourteen bits once to the left. With bit five set, the controller shifts the bits left once again. We start with ADC1 and shifting twice to the left. We power with a battery, turn on transmission at 256 SPS. We look at SCK to measure TCK and see 199-207 ns. The peak of our spectrum is 915 MHz. We see 240 SPS received. We have frequency_step = 1, which is suitable for DAC voltage 3.0 V, but we have DAC voltage 1.8 V on the A3054X, so we set frequency_step = 2. Reception rises to 252 SPS. On the transmitted signal we see average value 33023 cnt with noise 7.5 cnt rms.

We note that MSR and DC are not being set by our code, so we drive them LO, selecting AC coupling and GND connected to VC. We reprogram. With bench power 3.0 V quiescent current is 29 μA at 25°C. In our Faraday cage, running off a battery, we see 252 SPS and 7.5 cnt rms noise. The gain of our amplifier is ×62. Our VA = 1.82 V. Our input dynamic range is 30 mV. This 7.5 cnt is 3.4 μV rms. In the Neuroplayer, we filter 1-80 Hz and see 2.5 μV noise. In the noise we see traces of quantization, but no spikes. The spectrum is flat. In the noise sample below, we receive 251 samples, so fill in 5 to make 256. But there are more than five places where the signal stays at the same value from one sample to the next. These flat segments are quantization artifact.

We load external amplifiers that drive the X1-X4 inputs and load two BNC sockets. The amplifiers contain 100-kΩ resistors and with nothing connected to J1 or J2, we have 0V driving their inputs, which leads to current through the resistors, adding about 70 μA to quiescent current consumption of the board. We look at a frequency sweep. The gain at low frequencies is lower than we expect. We see relaxation in response to a 1-Hz square wave with time constant around 100 ms. We remove C14 and C15. We program with DC asserted. We should now have gain ×16 down to 0.0 Hz. We apply a square wave. We see the intact square on U18-1 and U18-3, but on Y1 we see relaxation with time constant around 300 ms. The DC gain is not zero, but is around ×5, while the gain at 10 Hz is around ×16. We perform a sinusoidal sweep, applying a 91-mVpp sine wave to X1 by delivering 100 mVpp with 1.8-V offset to the A3054X's DIN input. We leave CIN open circuit. In the center of the passband we see amplitude 55 kcnt, which is 1.5 Vpp at the amplifier output, or 94 mVpp at the amplifier input. The gain in the middle of the pass band is correct. It is the low-frequency gain that is wrong.

Amplitude We connect U21-6 directly to VC with a wire. We still see relaxation in square wave response. We repeat our sweep and obtain an identical response. We see VC moving up and down. The VC regulator can supply current, but it cannot sink current. Our external circuits on S3054X_4 do not draw current from VC = 0.9 V. Our amplifiers on S3054X_3 draw current when our X1-X3 and X4P inputs deviate from VC. When these are VC + 50 mV and DC is asserted, the total current flowing into VC will be 3 × (50 mV / 133 kΩ) for X1-X3 and 50 mV / 2.1 MΩ for X4P, making 1.1 μA in all. This will charge up C11, which has a nominal value of 22 μF but when we measure the capacitors, we get 13 μF. The charge rate will be 1.1 μA / 13 μF = 88 mV/s. Time constant is around 560 ms, expected corner frequency 0.28 Hz, which is pretty much exactly what we see in the plot above. One solution to this problem is to place a resistor from VC to 0V that draws enough current to supply the amplifier feedback networks. So long as the main feedback resistor is 2.0 MΩ, the feedback current can be as high as 0.9 V / 2.0 MΩ = 0.45 μA, so total could be 1.4 μA. This would add to our quiescent current. Another is to replace U17 with a resistor divider buffered by an op-amp. We might need a capacitor on the divider as well. We can fit the resistor on easily, there is space on section S4. The divider solution may not fit.

We note another problem with our A3054 design, in which we eliminate 1V8 and replace with VS. If we were to make this replacmenet, we would drive DC and MSR with VS = 3.0 V when the analog switches are powered by VA = 1.8 V. One way to solve this problem is to use VS to power the switches. We already have VS on section S3, and it will be no problem to bring VS to S4. We modify S3054A_3 to apply VS to all four switches and make the changes to the A305401A layout.

[09-APR-26] Connect 33 kΩ from VC to 0V. Relaxation of our square wave response disappears. We now get stable response down to 0.0 Hz. We repeat our sweep and call it "DC/91mV/0pF" to indicate DC input, 91-mV on X1, and C15 = 0 pF. We are using 100 mVpp sine wave with offset 1.75 V applied to J1 on A3054X, J2 open circuit. The 100 mVpp passes through 100 kΩ to the 1 MΩ input resistor of the X1 amplifier, and so drops to 91 mVpp. We load C15 = 220 pF and repeat the sweep. The amplitude is slightly lower in the pass-band. Load C15 = 100 pF and repeat. Switch to AC and apply 30 mVpp to J1 with the same 1.75 V offset.

The low-pass corner frequency for our amplifier with AC-coupling and no filter capacitor is about 160 Hz. We would like to provide up to 160 Hz for AC coupling, so we must eliminate the capacitor. With DC-coupling and no capacitor, the corner frequency is around 640 Hz. If we want to deliver 160 Hz with DC coupling we must take the average of four samples. The corner frequency we are seeing is due to the gain-bandwidth product of the OPA369, which is 12 kHz. We expect to see AC corner frequency 12 kHz / 62 = 190 Hz and DC corner frequency of 750 Hz. So long as we stick with the OPA369, we can allow the op-amp to perform our filtering for us. We can eliminate C15, C17, and C19.

We change resistors on external amplifiers for 1 MΩ, including those in series with our X1-X3. We remove R102 and let the common-mode voltage float at 0.9 V. Quiescent current is 33 μA at 25°C. We have 500 kΩ from VC to 0V across C11, consuming 1.8 μA. The external op-amps and resistors consume about 2.7 μA. The remaining 29.5 μAWe reprogram the board so that it transmits X1-X4 with AC coupling for channel numbers 1-4, and with DC coupling for channel numbers 5-8. With channel 9 we read the temperature sensor.

We sweep all the amplifiers. At this point, we change the vertical axis of our sweep plot to amplitude peak-to-peak. The X4 channel is DC-coupled. Our external circuits generate a differential signal with common mode voltage VC. The differential gain of the X4 amplifier is ×20. The input dynamic range is 1.8 V / 20 = 90 mV. For our 80-mV input we see output 60 kcnt peak-to-peak and we expect 65535 * 80 / 90 = 58 kcnt.

We have no low-pass filter capacitors on our op-amp feedback resistors. All low-pass corners are due to the OP369 itself, and are a frequencies inversely proportional to gain. We have adjusted the input amplitudes so that the amplifier output in the center of the pass band is close to 60 kcnt peak-to-peak for all of channels and configurations. The half-power frequency, which is a traditional measure of corner frequency for low-pass filters that roll off gradually, is the frequency at which the amplitude drops to roughly 42 kcnt pp. The AC-coupled X1-X3 have their corner at 160 Hz, the DC-coupled X1-X3 at 640 Hz, and the DC-coupled differential X4 at 500 Hz.

We remove R101. We have already removed R102. The fact that we are grounding our incoming test signals to 0V, but our amplifier ground is 0.9 V, has proved difficult. We now want to measure noise in isolation, so we disconnect these resistors and allow the inputs to be driven by our floating resistors. Input noise at 1024 SPS is 11 cnt rms = 5 μV rms in AC-coupled X1-X3, 9 cnt rms = 15 μV rms in DC-coupled X1-X3. In the DC-coupled signal's noise we see the quantization lines in an amplified picture. There are no random, large spikes.

We obtain the spectrum of X1 with AC coupling. With no filter, the noise amplitude is 5.0 μV rms. With low-pass filtering at 640, 320, 160, 80, and 40 Hz, the noise is 4.6, 4.0, 3.2, 2.4, and 1.7 μV rms.

We have on board a white LED in series with 1.0 kΩ that we can drive with our LED logic output. This output takes the place of ONL in our stimulator code, which still exists in P3054 V1.4, even including random stimuli. The lamp power modulator uses RCK to modulate the average light current from 0% to 100% in fifteen steps. We turn the LED on full power and take a look at the AC-coupled X1 signal, which is open-circuit.

We decrease the power to 50%. Now the lamp current is being modulated during the pulse. This modulation creates an additional new 140-μV pedestal artifact during the pulse.

We modify the P3054 software so that the lamp never gets turned on, but instead, whenever the stimulator code would turn on the lamp, it asserts MSR, leaving DC as it is. When we transmit a signal, we leave MSR as it is and construct DC and the input selection from the channel number. We load 16 kΩ for R30. When we assert MSR, GND drops by 7.14 mV. We remove R103, R104, and R105. We connect X1 to GND with 1.0 MΩ, X2 with 2.0 MΩ, and X3 with 16 kΩ. We measure the step down with MSR for AC and DC coupling on all three inputs. We calculate the electrode impedance from the size of the step.

It looks like we can measure the input impedance with a precision of better than ±1% of Z_in, which in our case is 1% of 1 MΩ, or ±10 kΩ. With AC coupling we get 20 kΩ for our 16 kΩ electrode impedance.

We see now that the impedance measurement circuit draws 0.9 V / 2 MΩ = 0.45 μA from 0.9 V. To support the amplifiers, we need to be able to provide a sink for 3 * 0.45 μA for X1-X3 and for X4 we might have X4N = X4P = 1.8 V, which would draw another 0.45 μA. That's almost 2 μA. If we drop R31 to 500 kΩ and R30 to 4 kΩ, we will have the same step size, almost 2 μA available to sink current out of VC, no additional components added to the circuit, and our VC remains stable as the resistors corrode. The additional cost is 1.5 μA over our original design. If we add an op-amp with 4-MΩ divider, we add around 1.2 μA and our VC will drift with corrosion of the divider. Quiescent current of the board at 25°C should be 29 μA.

[13-APR-26] We believe we have settled the A3054 circuit. Layout A305401A is complete. We will await netlist check, then submit for fabrication. We start work on a new text fixture board. We want to eliminate the external op-amps so we don't have to consider their current consumptikon. We will ground the incoming BNC signals to GND and test the amplifiers only when we have the circuit powered by a battery. We terminate the incoming signals with 51 Ω, then divide by 100 with 1 MΩ and 10 kΩ. We have J1 for the X1-X3 and X4P input. We have J2 for the X4N input. By applying opposite signals to X4P and X4N we can apply a purely differential signal to X4. Now we don't need any op-amps to shift or amplify or negate the incoming signals. We will have a 0V pad and a GND pad for scope probes. During MSR, we must be powered by battery. The VC potential will step down by 7.14 mV with respect to GND, as will VB, VS, and 0V.

[21-APR-26] Rigid-flex A305401A under review at fab house. We try inductor MBKK1608T4R7M, 4.7 μH in P0603 package. Prior to replacing the P0805 inductor we had loaded in place of L1, we see sustained and uniform 10-mVpp ripple, in which we have a sharp step up and a gradual decline. Quiescent current is 33 μA. We replace L1 and see ripple that is 12 mVpp but almost all steps are 4 mV with occasional 12 mV steps. Quiescent current is 33 μA. Telemetry reception is 98%, which is as good as it was before replacement.

[29-APR-26] Test fixture schematic S3054Y_1.gif complete. We have removed all the op-amps. The connector chassis and mouting holes are connected to GND. Unless we are measuring electrode impedance, GND will be connected by the A3054 IPT to VC. We have a battery holder on board that will accept a CR2032 battery to power the board. While programming, we will connect an external computer power supply ground to 0V. During programming, we must not connect DIN or CIN to a grounded signal generator. Doing so will short VC to 0V. Once the device is calibrated, we disconnect the programming connector and connect signals to DIN and CIN, which are divided by one hundred with respect to GND to create X and Y respectively. We connect X to X1, X2, X3, and X4P. We connect Y to X4N. We have an array of test points for all signals emerging from the two ten-way flex plugs on the IPT rigid-flex circuit. Printed circuit board A305402B now submitted for fabrication. Meanwhile, rigid-flex A305401A is in production.

[30-APR-26] We have loaded a white LED in D0402 package for D3. It flashes with the LED signal. We replace U4 while trying to figure out why LED is not being asserted, only to find later that we had disabled LED and instead enabled MSR in our software. Today we are seeing 20-mVpp ripple in 1V2. We are seeing failure to receive acknowledgement when transmission is off. We check the TXWP warm-up signal for the VCO and see it is working fine. When we transmit an acknowledgement without the transmit signal running, the TUNE voltage dips. This turns out to be because 1V8 is dipping. Inspection of the board reveals that C4, which decouples the 1V8 regulator U3 is missing. Restoring C4 fixes the problem, but we remain curious as to how 1V8 is stable during sustained 256 SPS transmission, but unstable when we perform a solitary transmission. With C4 restored we examine 1V2 once again and see a regular saw tooth with amplitude 15 mVpp.

[01-MAY-26] We measure 1V2 ripple with a ×1 probe and see 20 mVpp. We have for L1 MBKK1608T4R7M 4.7 μH P0603, 500 mA. We replace C3 and now see 9 mVpp. We are not sure what the previous C3 was, but we just loaded it with GRM158R61A226ME15D P0402 10V 22μ X5R ±20%. We replace with GRM158C80G226ME01D P0402 4V X6S ±20%. Ripple is now 8 mVpp. Reception 100%. Two hours later, ripple with no activity is 11 mVpp. Turn on transmission, 12 mVpp. Reception 100%.

We eliminate support for random stimuli and for modulated stimuli. Software drops to 2800 bytes and firmware drops to 1242 LUTs. Tag P3054 with v1.5. Wash circuit board, dry, and allow to cool. Ripple with no activity is 10 mVpp. Measure wake state battery current versus battery voltage and plot. Measure 256 SPS transmit current versus battery voltage: rises from 238 μA at 1.8 V to 252 μA at 4.0 V. At 3.0 V, 241 μA. The transmit current is mostly that current consumed by the temperature sensor, which we have configured to run continuously as fast as it can. In the A3054X, the sensors, clock, and crystal radio are all powered by 1V8.

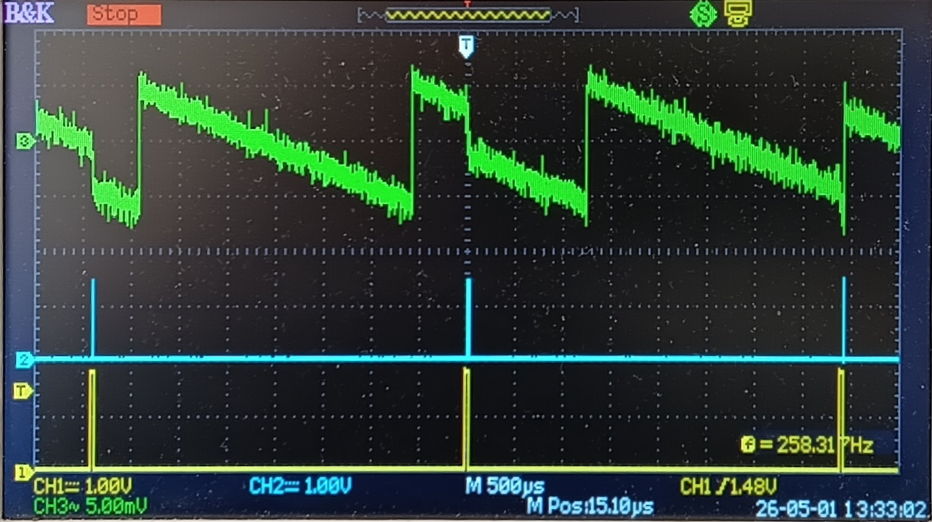

Disable the temperature sensor. Measure transmit current versus sample rate for five different signals: ACC, ADC, EEPROM, TEMP, and SYNC, for which we use channel numbers 11, 1, 10, 9, and 12 respectively. We have no accelerometer loaded, so sample cost is all in the logic and VCO. During SYNC we are not generating a stimulus. We measure the length of the interrupt service routine for each and get: 150 μs, 48 μs, 148 μs, 148 μs, and 44 μs respectively. In all cases, the VCO powers up for 8 μs.

The slopes are ACC: 0.148μA/SPS, ADC: 93 nA/SPS, EEPROM: 212 nA/SPS, TEMP: 151 nA/SPS, and SYNC: 90 nA/SPS. We assume worste-case A3048 0.120 μA/SPS even though in practice the value for the A3048 is 100 nA/SPS. Because we have no ACC, and the SYNC is internal to the logic, the difference between the ACC and SYNC slopes is due to 106 μs per sample additional time for which the CPU is in boost mode for the ACC readout compared to the SYNC readout. The slope difference is 58 nA/SPS. Battery current due to boost is 58 nA-s/sample / 106 μs/sample = 550 μA. This suggests 1V2 current is 550 μA * 3.0 V / 1.0 V * 0.8 = 1.3 mA, which is close to the 1.2 mA we estimate in the OSR8 Processor Manual. The SYNC slope of 90 nA/SPS consists of 44 μs of boost and 8 μs of VCO. The 44 μs of boost generates 24 nA/SPS, so the radio-frequency transmit is consuming 66 nA/SPS. Given that the VCO is on for 8 μs, this suggests the transmission draws 8.2 mA from the battery. The EEPROM reads consume an additional 64 nA/SPS compared to the ACC reads, which are of almost exactly the same length. Each EEPROM read consumes 64 nC of charge. We examine SCL and see the EEPROM read takes 104 μs, so the read current is 610 μA. The data sheet says maximum 1 mA. The temperature sensor consumes only 3 nA/SPS extra with the same 104-μs readout time, so its read current is of order 30 μA. The data sheet says typical 15 μA at 400 kHz. We are running at 500 kHz. The ADC readout consumes 3 nA/SPS more than the SYNC while taking 4 μs more in boost. The 4 μs at 550 μA accounts for 2.2 nA/SPS. The remaining 0.8 nA/SPS is reading out the ADC, although at this point our resolution of ±2 nA/SPS is greater than our quantity.

When transmitting ADC samples, we have two dominant sources of current consumption: 66 nA/SPS for transmission and 27 nA/SPS for CPU boost. The ADC conversion and readout are negligible. The ADC read takes only 5 μs of the 48 μs of the interrupt. The rest is pushing registers onto the stack and figuring out what the interrupt should do, which we count up to be around 160 clock cycles, or 32 μs at 5 MHz, plus 8 μs for transmit is 45 μs total, which compares well to our measured 48 μs.

We set up a temperature measurement counter that decrements one each pass through the main loop. When zero, the interrupt routine detects the zero and initiates a one-shot temperature measurement. The communication with the sensor must run in the interrupt so it will go fast and so that it will not be interrupted by some other I2C access. With the counter set to 65 we get a temperature measurement every 55 ms. At 128 SPS transmit of ADC our current consumption is 100 μA, up from 46 μA. The 18 Hz temperature readout is costing us 54 μA. The TMP117 data sheet says 1 Hz is typically 3.5 μA. We would like to try updating every two seconds, so we need a two-byte counter, counting down from 0x0900. With this implemented, we see roughly 0.5 Hz update and current is 47 μA for ADC readout, jumping up to 60 μA occasionally during measurement. In temperature transmission at 128 SPS, current is 56 μA. We see the reading changing every two seconds in the Receiver Instrument.

We are measuring current consumption at about 23°C. We expect the static current consumption of the logic chip to increase by 8 μA at 37°C. Our implanted current consumption for ADC sampling and transmission will therefore be our existing 36 μA at 23°C plus 8 μA is 44 μA. The transmission cost is 8 μs * 550 μA = 4.4 nC of boost plus 66 nC for the VCO = 70 nC. To read out an ADC and accumulate we need 5 μs of boost, or 2.5 nC. The ADC takes another 0.5 nC. If we do this 1024 times per second we have 3.0 μA overhead for any enabled channel.